# LM75A Digital temperature sensor and thermal watchdog Rev. 04 — 10 July 2007 Product data sheet

## 1. General description

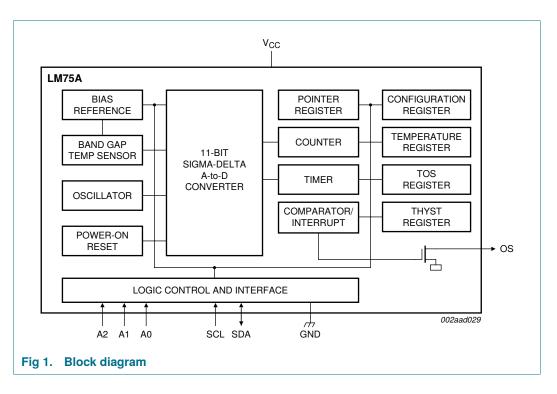

The LM75A is a temperature-to-digital converter using an on-chip band gap temperature sensor and Sigma-delta A-to-D conversion technique. The device is also a thermal detector providing an overtemperature detection output. The LM75A contains a number of data registers: Configuration register (Conf) to store the device settings such as device operation mode, OS operation mode, OS polarity and OS fault queue as described in <u>Section 7 "Functional description"</u>; temperature register (Temp) to store the digital temp reading, and set-point registers (Tos and Thyst) to store programmable overtemperature shutdown and hysteresis limits, that can be communicated by a controller via the 2-wire serial I<sup>2</sup>C-bus interface. The device also includes an open-drain output (OS) which becomes active when the temperature exceeds the programmed limits. There are three selectable logic address pins so that eight devices can be connected on the same bus without address conflict.

The LM75A can be configured for different operation conditions. It can be set in normal mode to periodically monitor the ambient temperature, or in shutdown mode to minimize power consumption. The OS output operates in either of two selectable modes: OS comparator mode or OS interrupt mode. Its active state can be selected as either HIGH or LOW. The fault queue that defines the number of consecutive faults in order to activate the OS output is programmable as well as the set-point limits.

The temperature register always stores an 11-bit 2's complement data giving a temperature resolution of 0.125 °C. This high temperature resolution is particularly useful in applications of measuring precisely the thermal drift or runaway.

The device is powered-up in normal operation mode with the OS in comparator mode, temperature threshold of 80 °C and hysteresis of 75 °C, so that it can be used as a stand-alone thermostat with those pre-defined temperature set points.

## 2. Features

- Pin-for-pin replacement for industry standard LM75 and offers improved temperature resolution of 0.125 °C and specification of a single part over power supply range from 2.8 V to 5.5 V

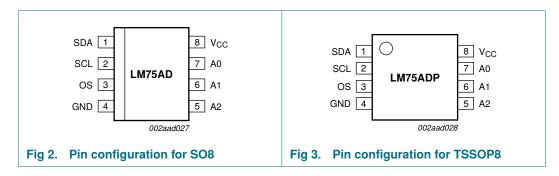

- Small 8-pin package types: SO8 and TSSOP8

- I<sup>2</sup>C-bus interface with up to 8 devices on the same bus

- Power supply range from 2.8 V to 5.5 V

- Temperatures range from –55 °C to +125 °C

- 11-bit ADC that offers a temperature resolution of 0.125 °C

- Temperature accuracy of:

- ◆ ±2 °C from –25 °C to +100 °C

- ◆ ±3 °C from –55 °C to +125 °C

- Programmable temperature threshold and hysteresis set points

- Supply current of 3.5 µA in shutdown mode for power conservation

- Stand-alone operation as thermostat at power-up

- ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115 and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

## 3. Applications

- System thermal management

- Personal computers

- Electronics equipment

- Industrial controllers

## 4. Ordering information

#### Table 1.Ordering information

| Type number | Package | Package                                                                |          |  |  |  |  |  |  |

|-------------|---------|------------------------------------------------------------------------|----------|--|--|--|--|--|--|

|             | Name    | Description                                                            | Version  |  |  |  |  |  |  |

| LM75AD      | SO8     | plastic small outline package; 8 leads;<br>body width 3.9 mm           | SOT96-1  |  |  |  |  |  |  |

| LM75ADP     | TSSOP8  | plastic thin shrink small outline package; 8 leads;<br>body width 3 mm | SOT505-1 |  |  |  |  |  |  |

### 4.1 Ordering options

### Table 2.Ordering options

| Type number | Topside mark | Temperature range                              |

|-------------|--------------|------------------------------------------------|

| LM75AD      | LM75A        | $T_{amb} = -55 \text{ °C to } +125 \text{ °C}$ |

| LM75ADP     | L75A         | $T_{amb} = -55 \text{ °C to } +125 \text{ °C}$ |

**LM75A**

### Digital temperature sensor and thermal watchdog

## 5. Block diagram

## 6. Pinning information

### 6.1 Pinning

## 6.2 Pin description

| Table 3. | Pin description |                                                                               |

|----------|-----------------|-------------------------------------------------------------------------------|

| Symbol   | Pin             | Description                                                                   |

| SDA      | 1               | Digital I/O. I <sup>2</sup> C-bus serial bidirectional data line; open-drain. |

| SCL      | 2               | Digital input. I <sup>2</sup> C-bus serial clock input.                       |

| OS       | 3               | Overtemp Shutdown output; open-drain.                                         |

| GND      | 4               | Ground. To be connected to the system ground.                                 |

| A2       | 5               | Digital input. User-defined address bit 2.                                    |

| Table 3.        | Pin descriptioncontinued |                                            |  |  |  |  |  |

|-----------------|--------------------------|--------------------------------------------|--|--|--|--|--|

| Symbol          | Pin Description          |                                            |  |  |  |  |  |

| A1              | 6                        | Digital input. User-defined address bit 1. |  |  |  |  |  |

| A0              | 7                        | Digital input. User-defined address bit 0. |  |  |  |  |  |

| V <sub>CC</sub> | 8                        | Power supply.                              |  |  |  |  |  |

## 7. Functional description

### 7.1 General operation

The LM75A uses the on-chip band gap sensor to measure the device temperature with the resolution of 0.125 °C and stores the 11-bit 2's complement digital data, resulted from 11-bit A-to-D conversion, into the device Temp register. This Temp register can be read at any time by a controller on the l<sup>2</sup>C-bus. Reading temperature data does not affect the conversion in progress during the read operation.

The device can be set to operate in either mode: normal or shutdown. In normal operation mode, the temp-to-digital conversion is executed every 100 ms and the Temp register is updated at the end of each conversion. In shutdown mode, the device becomes idle, data conversion is disabled and the Temp register holds the latest result; however, the device l<sup>2</sup>C-bus interface is still active and register write/read operation can be performed. The device operation mode is controllable by programming bit B0 of the configuration register. The temperature conversion is initiated when the device is powered-up or put back into normal mode from shutdown.

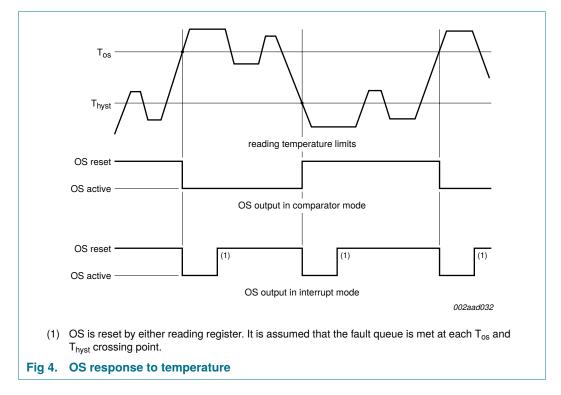

In addition, at the end of each conversion in normal mode, the temperature data (or Temp) in the Temp register is automatically compared with the overtemperature shutdown threshold data (or Tos) stored in the Tos register, and the hysteresis data (or Thyst) stored in the Thyst register, in order to set the state of the device OS output accordingly. The device Tos and Thyst registers are write/read capable, and both operate with 9-bit 2's complement digital data. To match with this 9-bit operation, the Temp register uses only the 9 MSB bits of its 11-bit data for the comparison.

The way that the OS output responds to the comparison operation depends upon the OS operation mode selected by configuration bit B1, and the user-defined fault queue defined by configuration bits B3 and B4.

In OS comparator mode, the OS output behaves like a thermostat. It becomes active when the Temp exceeds the  $T_{os}$ , and is reset when the Temp drops below the  $T_{hyst}$ . Reading the device registers or putting the device into shutdown does not change the state of the OS output. The OS output in this case can be used to control cooling fans or thermal switches.

In OS interrupt mode, the OS output is used for thermal interruption. When the device is powered-up, the OS output is first activated only when the Temp exceeds the  $T_{os}$ ; then it remains active indefinitely until being reset by a read of any register. Once the OS output has been activated by crossing  $T_{os}$  and then reset, it can be activated again only when the Temp drops below the  $T_{hyst}$ ; then again, it remains active indefinitely until being reset by a read of any register. The OS interrupt operation would be continued in this sequence:  $T_{os}$  trip, Reset,  $T_{hyst}$  trip, Reset,  $T_{os}$  trip, Reset, etc.

In both cases, comparator mode and interrupt mode, the OS output is activated only if a number of consecutive faults, defined by the device fault queue, has been met. The fault queue is programmable and stored in the two bits, B3 and B4, of the Configuration register. Also, the OS output active state is selectable as HIGH or LOW by setting accordingly the configuration register bit B2.

At power-up, the device is put into normal operation mode, the  $T_{os}$  is set to 80 °C, the  $T_{hyst}$  is set to 75 °C, the OS active state is selected LOW and the fault queue is equal to 1. The temp reading data is not available until the first conversion is completed in about 100 ms.

The OS response to the temperature is illustrated in Figure 4.

## 7.2 I<sup>2</sup>C-bus serial interface

The LM75A can be connected to a compatible 2-wire serial interface I<sup>2</sup>C-bus as a slave device under the control of a controller or master device, using two device terminals, SCL and SDA. The controller must provide the SCL clock signal and write/read data to/from the device through the SDA terminal. Notice that if the I<sup>2</sup>C-bus common pull-up resistors have not been installed as required for I<sup>2</sup>C-bus, then an external pull-up resistor, about 10 k $\Omega$ , is needed for each of these two terminals. The bus communication protocols are described in Section 7.10.

### 7.3 Slave address

The LM75A slave address on the I<sup>2</sup>C-bus is partially defined by the logic applied to the device address pins A2, A1 and A0. Each of them is typically connected either to GND for logic 0, or to  $V_{CC}$  for logic 1. These pins represent the three LSB bits of the device 7-bit address. The other four MSB bits of the address data are preset to '1001' by hard wiring inside the LM75A. Table 4 shows the device's complete address and indicates that up to

8 devices can be connected to the same bus without address conflict. Because the input pins, SCL, SDA and A2 to A0, are not internally biased, it is important that they should not be left floating in any application.

|     | <b>Address t</b><br>; 0 = LOW. | able |   |    |    |     |

|-----|--------------------------------|------|---|----|----|-----|

| MSB |                                |      |   |    |    | LSB |

| 1   | 0                              | 0    | 1 | A2 | A1 | A0  |

### 7.4 Register list

The LM75A contains four data registers beside the pointer register as listed in <u>Table 5</u>. The pointer value, read/write capability and default content at power-up of the registers are also shown in <u>Table 5</u>.

| Table 5.         | Registe          | r table   |              |                                                                                                                                                          |

|------------------|------------------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register<br>name | Pointer<br>value | R/W       | POR<br>state | Description                                                                                                                                              |

| Conf             | 01h              | R/W       | 00h          | Configuration register: contains a single 8-bit data byte; to set the device operating condition; default = 0.                                           |

| Temp             | 00h              | read only | n/a          | Temperature register: contains two 8-bit data bytes; to store the measured Temp data.                                                                    |

| Tos              | 03h              | R/W       | 5000h        | Overtemperature shutdown threshold register:<br>contains two 8-bit data bytes; to store the<br>overtemperature shutdown $T_{os}$ limit; default = 80 °C. |

| Thyst            | 02h              | R/W       | 4B00h        | Hysteresis register: contains two 8-bit data bytes; to store the hysteresis $T_{hyst}$ limit; default = 75 °C.                                           |

### 7.4.1 Pointer register

The Pointer register contains an 8-bit data byte, of which the two LSB bits represent the pointer value of the other four registers, and the other 6 MSB bits are equal to 0, as shown in <u>Table 6</u> and <u>Table 7</u>. The Pointer register is not accessible to the user, but is used to select the data register for write/read operation by including the pointer data byte in the bus command.

| Table 6. | Pointer    | ter register |    |    |    |               |  |

|----------|------------|--------------|----|----|----|---------------|--|

| B7       | <b>B</b> 6 | B5           | B4 | B3 | B2 | B[1:0]        |  |

| 0        | 0          | 0            | 0  | 0  | 0  | pointer value |  |

| Table 7. | Pointer | value                                   |

|----------|---------|-----------------------------------------|

| B1       | B0      | Selected register                       |

| 0        | 0       | Temperature register (Temp)             |

| 0        | 1       | Configuration register (Conf)           |

| 1        | 0       | Hysteresis register (Thyst)             |

| 1        | 1       | Overtemperature shutdown register (Tos) |

Because the Pointer value is latched into the Pointer register when the bus command (which includes the pointer byte) is executed, a read from the LM75A may or may not include the pointer byte in the statement. To read again a register that has been recently read and the pointer has been preset, the pointer byte does not have to be included. To

read a register that is different from the one that has been recently read, the pointer byte must be included. However, a write to the LM75A must always include the pointer byte in the statement. The bus communication protocols are described in Section 7.10.

At power-up, the Pointer value is equal to 0 and the Temp register is selected; users can then read the Temp data without specifying the pointer byte.

### 7.4.2 Configuration register

The Configuration register (Conf) is a write/read register and contains an 8-bit non-complement data byte that is used to configure the device for different operation conditions. Table 8 shows the bit assignments of this register.

| Table 8.  | Conf register    |

|-----------|------------------|

| Legend: * | = default value. |

| Bit    | Symbol        | Access | Value | Description                                                                    |

|--------|---------------|--------|-------|--------------------------------------------------------------------------------|

| B[7:5] | reserved      | R/W    | 000*  | reserved for manufacturer's use; should be kept as zeroes for normal operation |

| B[4:3] | OS_F_QUE[1:0] | R/W    |       | OS fault queue programming                                                     |

|        |               |        | 00*   | queue value = 1                                                                |

|        |               |        | 01    | queue value = 2                                                                |

|        |               |        | 10    | queue value = 4                                                                |

|        |               |        | 11    | queue value = 6                                                                |

| B2     | OS_POL        | R/W    |       | OS polarity selection                                                          |

|        |               |        | 0*    | OS active LOW                                                                  |

|        |               |        | 1     | OS active HIGH                                                                 |

| B1     | OS_COMP_INT   | R/W    |       | OS operation mode selection                                                    |

|        |               |        | 0*    | OS comparator                                                                  |

|        |               |        | 1     | OS interrupt                                                                   |

| B0     | SHUTDOWN      | R/W    |       | device operation mode selection                                                |

|        |               |        | 0*    | normal                                                                         |

|        |               |        | 1     | shutdown                                                                       |

### 7.4.3 Temperature register

The Temperature register (Temp) holds the digital result of temperature measurement or monitor at the end of each analog-to-digital conversion. This register is read-only and contains two 8-bit data bytes consisting of one Most Significant Byte (MSByte) and one Least Significant Byte (LSByte). However, only 11 bits of those two bytes are used to store the Temp data in 2's complement format with the resolution of 0.125 °C. <u>Table 9</u> shows the bit arrangement of the Temp data in the data bytes.

| Table | 9.  | Temp   | regist | er |    |    |    |    |    |    |   |   |   |   |   |

|-------|-----|--------|--------|----|----|----|----|----|----|----|---|---|---|---|---|

| MSBy  | /te | LSByte |        |    |    |    |    |    |    |    |   |   |   |   |   |

| 7     | 6   | 5      | 4      | 3  | 2  | 1  | 0  | 7  | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

| D10   | D9  | D8     | D7     | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Х | Х | Х | Х | Х |

When reading register Temp, all 16 bits of the two data bytes (MSByte and LSByte) are provided to the bus and must be all collected by the controller to complete the bus operation. However, only the 11 most significant bits should be used, and the 5 least significant bits of the LSByte are zero and should be ignored. One of the ways to calculate the Temp value in °C from the 11-bit Temp data is:

- 1. If the Temp data MSByte bit D10 = 0, then the temperature is positive and Temp value (°C) = +(Temp data) × 0.125 °C.

- If the Temp data MSByte bit D10 = 1, then the temperature is negative and Temp value (°C) = -(2's complement of Temp data) × 0.125 °C.

Examples of the Temp data and value are shown in Table 10.

| 11-bit binary<br>(2's complement) | Hexadecimal value | Decimal value | Value       |

|-----------------------------------|-------------------|---------------|-------------|

| 011 1111 1000                     | 3F8               | 1016          | +127.000 °C |

| 011 1111 0111                     | 3F7               | 1015          | +126.875 °C |

| 011 1111 0001                     | 3F1               | 1009          | +126.125 °C |

| 011 1110 1000                     | 3E8               | 1000          | +125.000 °C |

| 000 1100 1000                     | 0C8               | 200           | +25.000 °C  |

| 000 0000 0001                     | 001               | 1             | +0.125 °C   |

| 000 0000 0000                     | 000               | 0             | 0.000 °C    |

| 111 1111 1111                     | 7FF               | -1            | –0.125 °C   |

| 111 0011 1000                     | 738               | -200          | –25.000 °C  |

| 110 0100 1001                     | 649               | -439          | –54.875 °C  |

| 110 0100 1000                     | 648               | -440          | –55.000 °C  |

#### Table 10. Temp register value

Obviously, for 9-bit Temp data application in replacing the industry standard LM75, just use only 9 MSB bits of the two bytes and disregard 7 LSB of the LSByte. The 9-bit Temp data with 0.5 °C resolution of the LM75A is defined exactly in the same way as for the standard LM75 and it is here similar to the Tos and Thyst registers.

### 7.4.4 Overtemperature shutdown threshold (Tos) and hysteresis (Thyst) registers

These two registers, are write/read registers, and also called set-point registers. They are used to store the user-defined temperature limits, called overtemperature shutdown threshold (Tos) and hysteresis temperature (Thyst), for the device watchdog operation. At the end of each conversion the Temp data will be compared with the data stored in these two registers in order to set the state of the device OS output; see Section 7.1.

Each of the set-point registers contains two 8-bit data bytes consisting of one MSByte and one LSByte the same as register Temp. However, only 9 bits of the two bytes are used to store the set-point data in 2's complement format with the resolution of 0.5 °C. <u>Table 11</u> and <u>Table 12</u> show the bit arrangement of the Tos data and Thyst data in the data bytes.

Notice that because only 9-bit data are used in the set-point registers, the device uses only the 9 MSB of the Temp data for data comparison.

| MSB                       | yte |            |             |          |    |    |    | LSBy | te              |   |   |   |   |   |   |

|---------------------------|-----|------------|-------------|----------|----|----|----|------|-----------------|---|---|---|---|---|---|

| 7                         | 6   | 5          | 4           | 3        | 2  | 1  | 0  | 7    | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

| D8                        | D7  | D6         | D5          | D4       | D3 | D2 | D1 | D0   | Х               | Х | Х | Х | Х | Х | Х |

| <b>T</b> able             | 12. | Thyst      | reaist      | ter      |    |    |    |      |                 |   |   |   |   |   |   |

|                           |     | Thyst      | regist      | ter      |    |    |    | LSBy | te              |   |   |   |   |   |   |

| <b>Fable</b><br>MSBy<br>7 |     | Thyst<br>5 | regist<br>4 | ter<br>3 | 2  | 1  | 0  | LSBy | t <b>e</b><br>6 | 5 | 4 | 3 | 2 | 1 | 0 |

When a set-point register is read, all 16 bits are provided to the bus and must be collected by the controller to complete the bus operation. However, only the 9 most significant bits should be used and the 7 LSB of the LSByte are equal to zero and should be ignored.

Table 13 shows examples of the limit data and value.

#### Table 13. Tos and Thyst limit data and value

| 11-bit binary<br>(2's complement) | Hexadecimal value | Decimal value | Value     |

|-----------------------------------|-------------------|---------------|-----------|

| 0 1111 1010                       | 0FA               | 250           | +125.0 °C |

| 0 0011 0010                       | 032               | 50            | +25.0 °C  |

| 0 0000 0001                       | 001               | 1             | +0.5 °C   |

| 0 0000 0000                       | 000               | 0             | 0.0 °C    |

| 1 1111 1111                       | 1FF               | -1            | –0.5 °C   |

| 1 1100 1110                       | 1CE               | -50           | –25.0 °C  |

| 1 1001 0010                       | 192               | -110          | −55.0 °C  |

### 7.5 OS output and polarity

The OS output is an open-drain output and its state represents results of the device watchdog operation as described in Section 7.1. In order to observe this output state, an external pull-up resistor is needed. The resistor should be as large as possible, up to 200 k $\Omega$ , to minimize the Temp reading error due to internal heating by the high OS sinking current.

The OS output active state can be selected as HIGH or LOW by programming bit B2 (OS\_POL) of register Conf: setting bit OS\_POL to logic 1 selects OS active HIGH and setting bit B2 to logic 0 sets OS active LOW. At power-up, bit OS\_POL is equal to logic 0 and the OS active state is LOW.

### 7.6 OS comparator and interrupt modes

As described in <u>Section 7.1</u>, the device OS output responds to the result of the comparison between register Temp data and the programmed limits, in registers Tos and Thyst, in different ways depending on the selected OS mode: OS comparator or OS interrupt. The OS mode is selected by programming bit B1 (OS\_COMP\_INT) of register Conf: setting bit OS\_COMP\_INT to logic 1 selects the OS interrupt mode, and setting to logic 0 selects the OS comparator mode. At power-up, bit OS\_COMP\_INT is equal to logic 0 and the OS comparator is selected.